## ECE 695 Numerical Simulations Lecture 35: Solar Hybrid Energy Conversion Systems

Prof. Peter Bermel April 12, 2017

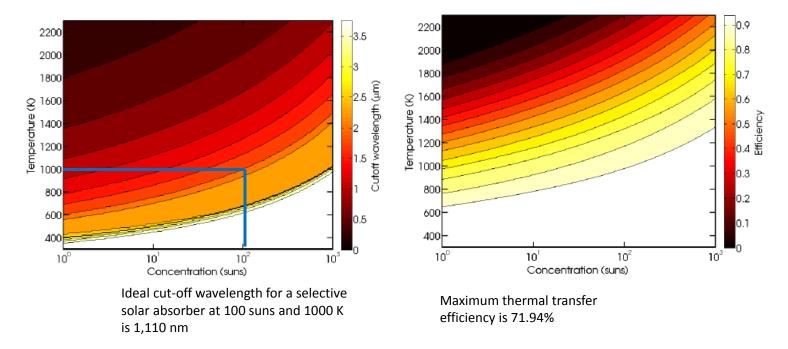

#### **Ideal Selective Solar Absorber – Efficiency Limits**

Bermel, Peter, et al. "Selective solar absorbers." Annual Review of Heat Transfer 15.15 (2012).

## Selective Solar Absorbers at T=1000 K (100 suns)

ECE 695, Prof. Bermel

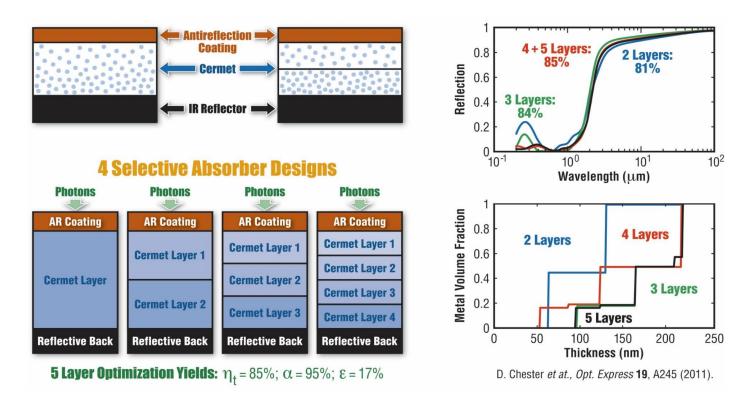

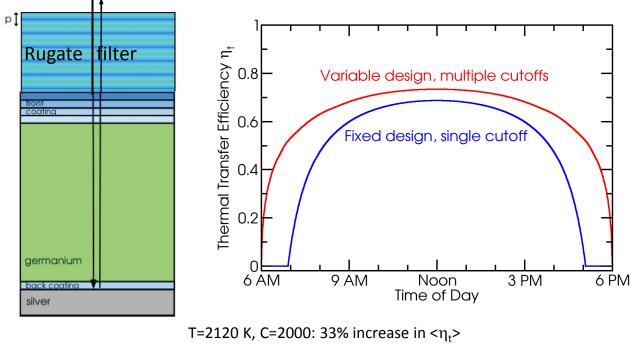

## Outperformance of Tunable Ideal Selective Absorbers

16.5% increase in energy generation/day

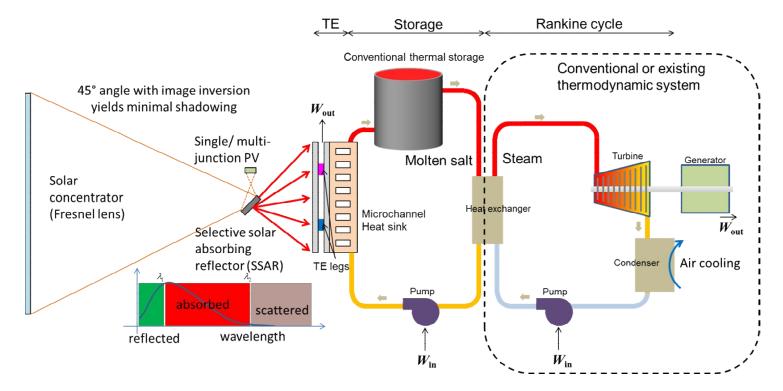

#### **Solar PV/Thermal Hybrid Conversion**

Spectral splitting advantages:

- Puts each photon to its best use

- Adds cheap storage

- Reduces PV heating

Thermal storage Electricity Turbine mental Dispatchability 50% from solar

Concentrated Solar

SSS

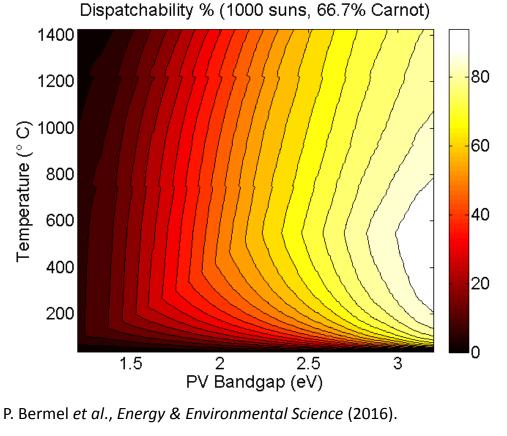

P. Bermel *et al., Energy & Environmental Science* (2016).

ECE 695, Prof. Bermel

4/12/2017

Radiation loss  $\rightarrow 0$ **800**-

1073°C

TE

550°C

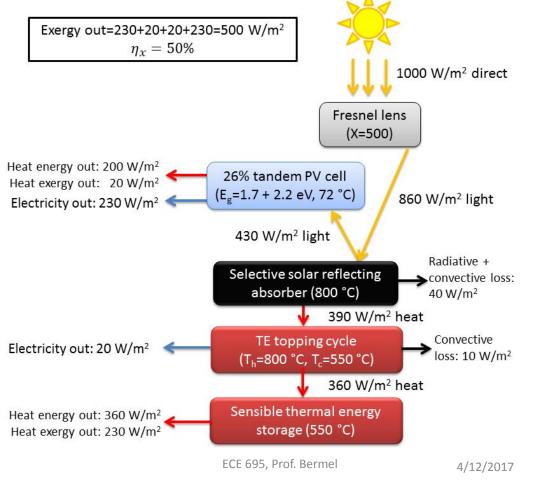

### Efficient Solar PV/Thermal Hybrid Conversion

ECE 695, Prof. Bermel

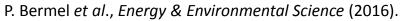

### Thermoelectric Topping Cycles Stabilize Efficiency Above 550 °C

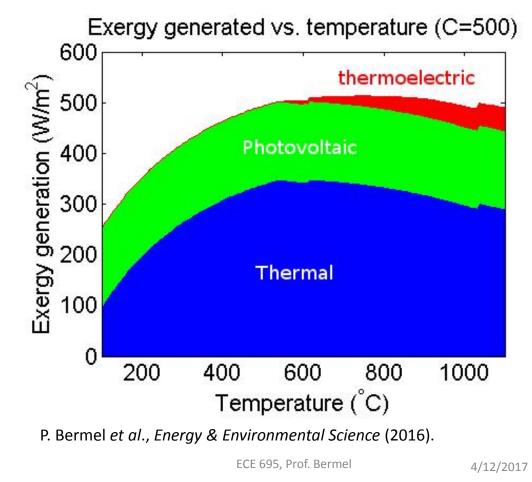

# Optimal PV Bandgap Around 2.1 eV for 500 suns

8

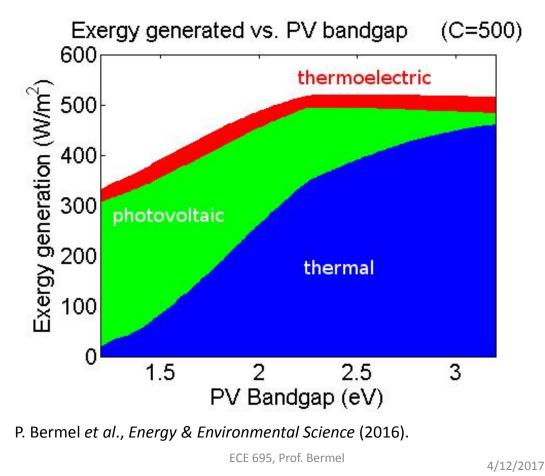

## Solar PV/Thermal Hybrid Conversion Efficiency

ECE 695, Prof. Bermel

# Solar PV/Thermal Hybrid Conversion Dispatchability

ECE 695, Prof. Bermel

## Efficient Solar PV/Thermal Hybrid Conversion

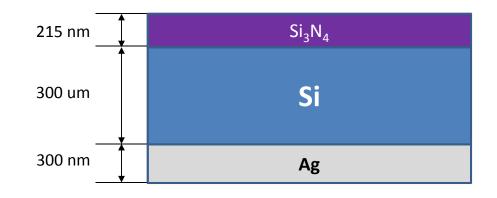

# **Selective Solar Absorbers**

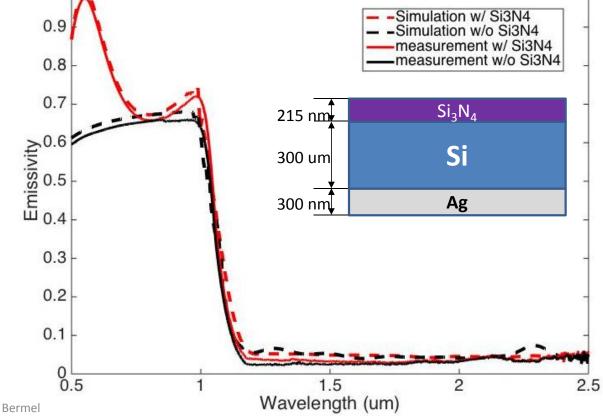

Schematic of the structure for selective absorber based on Si substrate with 215nm  $Si_3N_4$  front antireflection coating (ARC) and 300nm Ag back reflection layer. Heights are not to scale.

H. Tian et al., Appl. Phys. Lett. (2017)

4/12/2017

# **Method - Fabrication**

- Si3N4: PVD Sputtering: a magnetron sputtering system with unheated stage (custom built by PVD Products). The condition of the sputtering is 100w, 5mTorr, 15sccm Ar. 7rpm rotation of the stage. The deposition time is 86min around 200-215nm, as determined by spectroscopic ellipsometry (Filmetrics).

- Ag: CHA evaporation: Deposition rate is 1.5 Å/s (as determined by a quartz crystal monitor) for around half an hour until 300 nm.

- Si substrate: N type (Phos), 2 inch, <100>, 254-304um thickness, double side polished, with resistivity 10-20 Ω·cm (Pure Wafer).

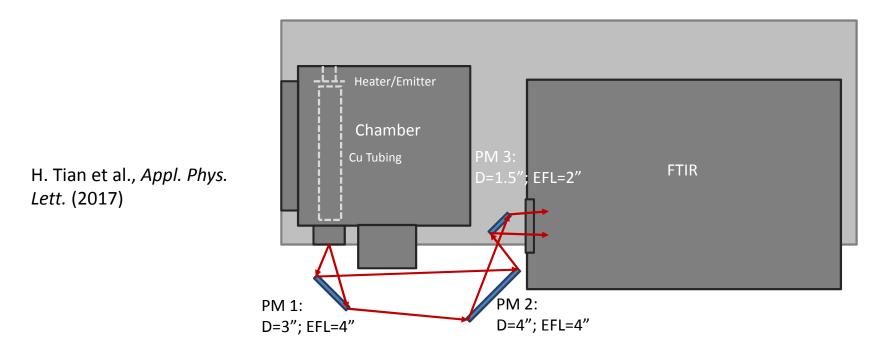

## **Direct Thermal Emission Measurement System**

The sample is heated by the heater, and the emitted light is collected and guided by the Cu tube, transmitted through a CaF<sub>2</sub> window, reflected by three off-axis parabolic mirrors (PM 1, 2, and 3, Edmund Optics) to a Fourier Transform InfraRed (FTIR) spectrometer with a mercury cadmium telluride detector and KBr beam splitter (Thermo Fisher Nicolet 670).

4/12/2017

#### 300 µm Si Experiment & Simulation at Room Temperature

Measurement (solid lines) and simulation (dashed lines) of the emissivity of selective absorbers with (red lines) and without (black lines) front coating at room temperature. Measurements performed by a Lambda 950 spectrophotometer with an integrating sphere (Labsphere). The thicknesses of  $Si_3N_4$ , Si and Ag are 215nm, 300 µm and 300nm respectively.

H. Tian et al., Appl. Phys. Lett. (2017)

4/12/2017

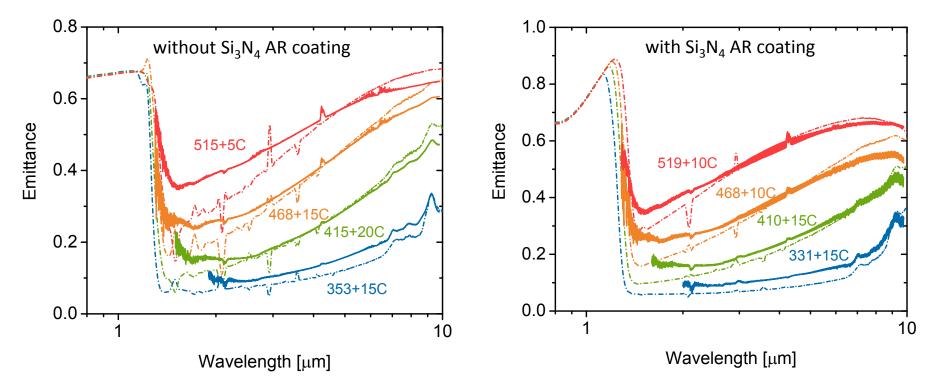

#### 300 $\mu$ m Si Experiment & Simulation at High Temperatures

High spectral selectivity is observed at 468 °C in both samples, with a cutoff wavelength of approximately 1.3  $\mu$ m. Higher short-wavelength emittance is both predicted and observed for the structure with a Si<sub>3</sub>N<sub>4</sub> AR coating

4/12/2017

H. Tian et al., Appl. Phys. Lett. (2017)

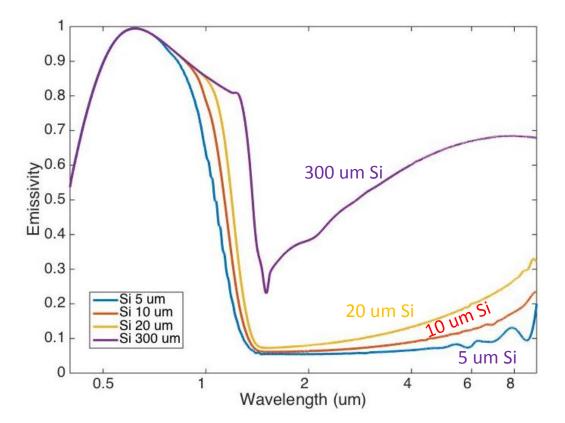

# Thin Si film optimization targeted @ 550 ° C

Emissivity for selective absorbers with different Si thicknesses. Optimal  $Si_3N_4$  thickness is used for each curve which is 80 nm. The temperature is set at 550°C and the F-P interference around the Mid-IR is smoothed out for more clear comparison. Less MWIR absorption is experienced for thinner layers of silicon because all samples are in the intrinsic regime, and free carrier absorption dominates.

H. Tian et al., Appl. Phys. Lett. (2017)

4/12/2017

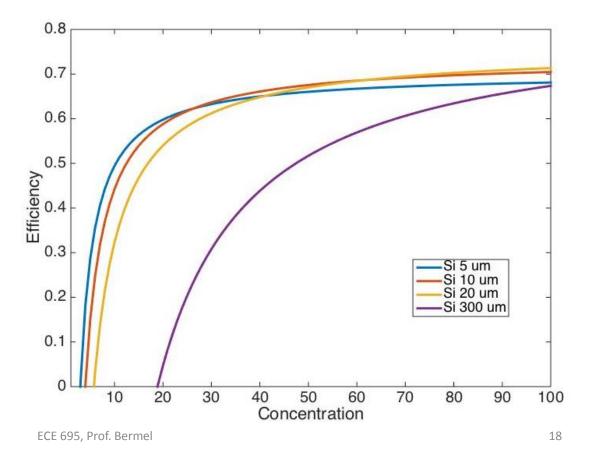

## **Optimization Summary for 550 ° C**

Dependence of solar thermal transfer efficiency  $\eta_t$  for different Si thicknesses on the concentration. The Si<sub>3</sub>N<sub>4</sub> thickness is fixed at 80nm, and the temperature is 550C. Thinner layers of silicon experience less reradiation; however layers which are too thin have less absorption, which puts an upper bound on  $\eta_t$ .

H. Tian et al., Appl. Phys. Lett. (2017)

4/12/2017

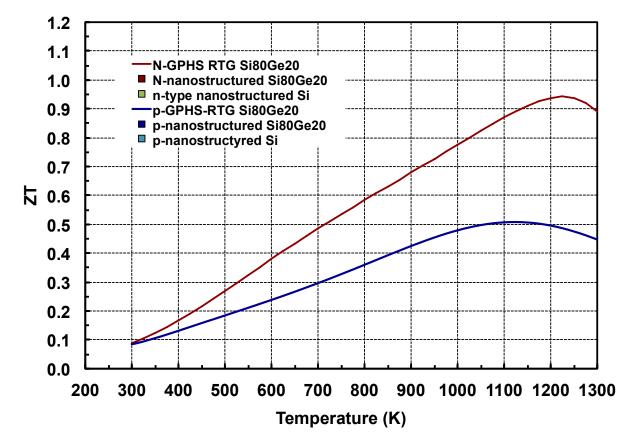

### Thermoelectric Figure of Merit ZT: Silicon and Silicon Germanium ZT vs. T

ECE 695, Prof. Bermel

### Solar PV/Thermal Conversion **Efficiency with Improved TE**

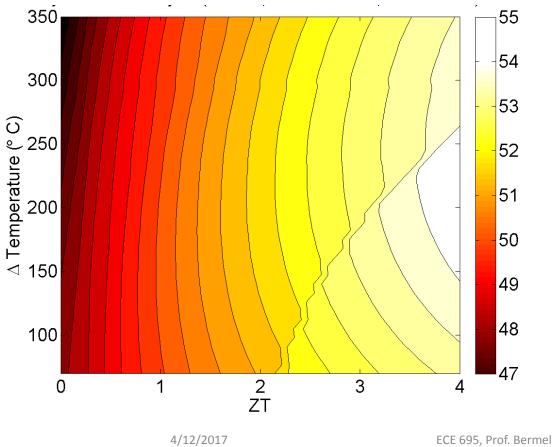

Calculated system exergy as a function of the selective solar surface (SSS) temperature differential (75-350  $^{\circ}$  C) and the ZT value of the thermoelectrics. We assumed 500x solar concentration. As one goes from no thermoelectrics to ZT=4, an overall improvement of 8% can be achieved. These calculations take into account reradiation losses at high SSS temperatures

> P. Bermel et al., Energy & Environmental Science (2016).

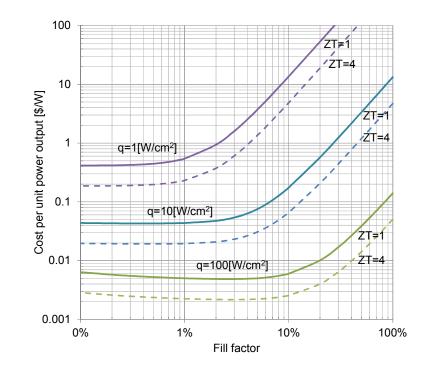

Cost per power output \$/W as a function of fill factor for ZT=1 and 4, and heat fluxes which reflect the heat sink performances. This graph assumes a maximum temperature of 2300K and ambient temperature of 310K, with the TE material price \$500/kg, and substrate \$26/kg.

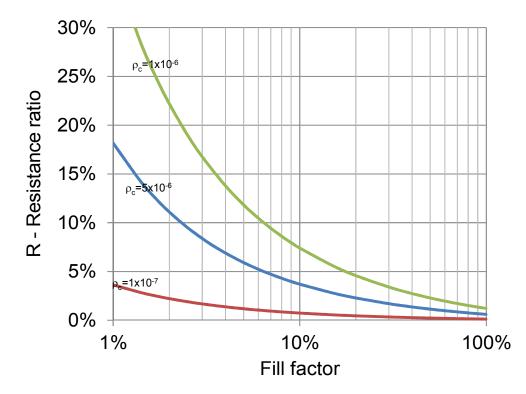

Ratio of parasitic electrical resistance to entire resistance as a function of Fill factor, with a variation of specific contact resistivity [Ohm.cm<sup>2</sup>]. Conditions are for 1000 elements per 1cm<sup>2</sup> module.

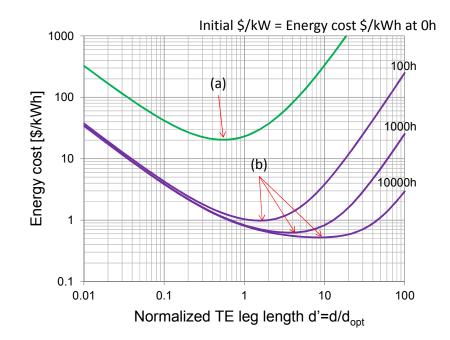

Energy cost vs. normalized leg length, assuming the same parameters as before. Thicker TE legs cause higher efficiency but reduced power output. The economical optimum exists in between the design for maximum power output and maximum efficiency.

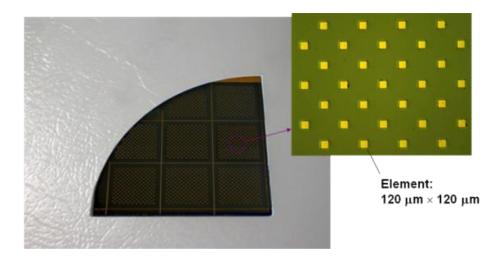

Six full element array chips were fabricated on the quarter wafer. Each element array chip contains 200 elements, and area size of each element is 120  $\mu$ m × 120  $\mu$ m.

4/12/2017

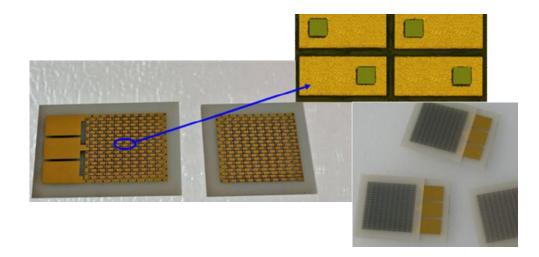

400 elements of 200 n-ErAs:InGaAlAs and 200 p-ErAs:InGaAs elements, 10  $\mu$ m thick, were bonded on the upper and lower AlN plates via wafer scale approach and flip-chip bonding technique.

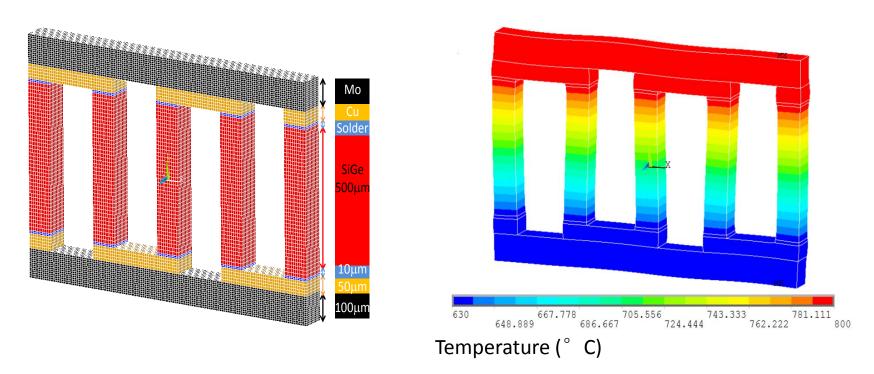

Thermomechanical 2D simulation for a 5-leg TE module in ANSYS. The TE material is SiGe, and the substrates are Molybdenum. The largest stress at interfaces is on the order of 56 MPa ( $\Delta$ T = 170 °C) in share stress (horizontal-direction)

## Next Class

#### Next time, we will discuss engineering grand challenge problems, and what role simulations can play in addressing them