## **TRC1000 Reconde v1.1** Xilinx ISE 14.7 Tutorial

## Sangjun Eom

Date: 7.10.2018

### **Table of Contents**

- 1. Hardware Setup

- 2. Copy an Existing Project

- A. Test the Project

- a. Open the Project on Xilinx Platform Studio

- b. Import the Project to Xilinx SDK

- c. Program the Hardware

- **B. Modify the Project**

- a. Add a New Software Module

- b. Add a New IP Core (Add / Change Wedges)

- c. Create a New IP Core

- 3. Create a New Project

- 4. Troubleshooting

### HARDWARE SETUP

#### 1. CPU and I/O

The RecoNode is a reconfigurable computational node for creating heterogeneous wireless control networks.

Each node includes a hard-core PowerPC CPU (reconfigurable software), an FPGA (reconfigurable computational hardware), and two MorphingBus peripheral I/O buses (reconfigurable I/O hardware).

From 1 to n nodes can be configured to create an integrated control network using PBO/RT software.

### **1. Hardware Setup**

You can either use...

- New RecoNode TRC1000 v1.1 (S/N 200 215)

- Old RecoNode TRC1000 v1.0 (S/N 000 199)

Both RecoNode versions 1.1 and 1.0 are based on the Xilinx Virtex4 FPGA with onboard PROM and DRAM.

The MorphingBus depends on the configuration of the FPGA for proper operation, so we have a few "standard I/O stacks" to make start-up easy.

See the RecoNode Morphing Bus manual for I/O options.

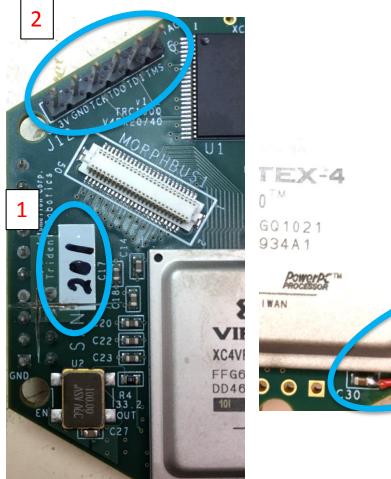

### 1. Identifying a Good RecoNode v1.1

3

#### **TRC1000 v1.1** SN # 200 - 215

The RecoNode PCB includes some routing errors that must be fixed with "blue wires" for proper operation for either v1.0 or v1.1. If your RecoNode has a serial number (Fig. 1), it should be ready to go.

Some indicators of fixes include:

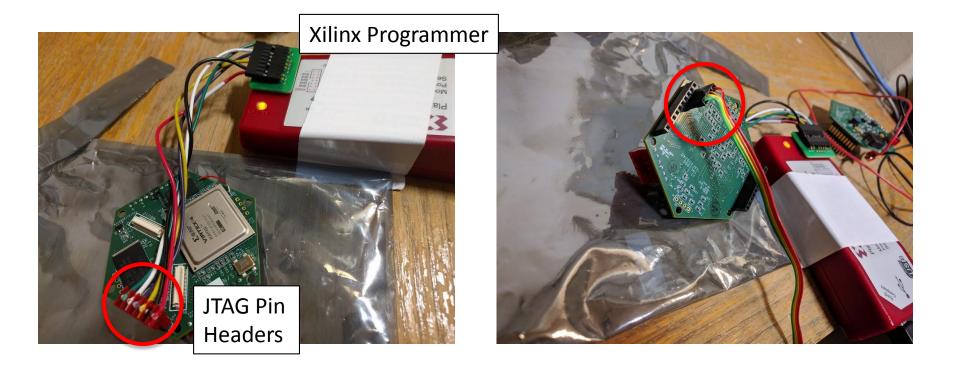

- JTAG plug has been relocated to bottom side (Fig. 2)

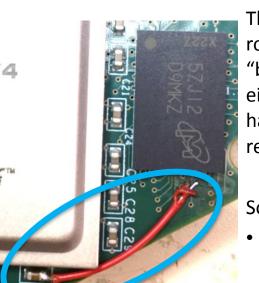

- Power wire added to DRAM (Fig. 3)

### **1. Hardware Setup**

Connect Xilinx Programmer to JTAG Pin Headers on RecoNode Connect UART to UART Pin Headers (J5) located on bottom side of RecoNode

### **1. Hardware Setup**

Supply **3.7** Volts to the power board. TRC 1000 should be connected to JTAG, serial communication cable, and power board

If (The board is not programmed) then If the current is around 0.2 – 0.3 A then Pass, it is good If the current is > 0.3 A, then Turn off the power supply. Something might be shorted.

If (The chip is programmed) then If The current rises from 0.2 – 0.3 A to 0.5 – 0.6 A. then Pass, it is good If the current is > ~0.65 A - after programmed then Turn off the power supply. Something might be shorted.

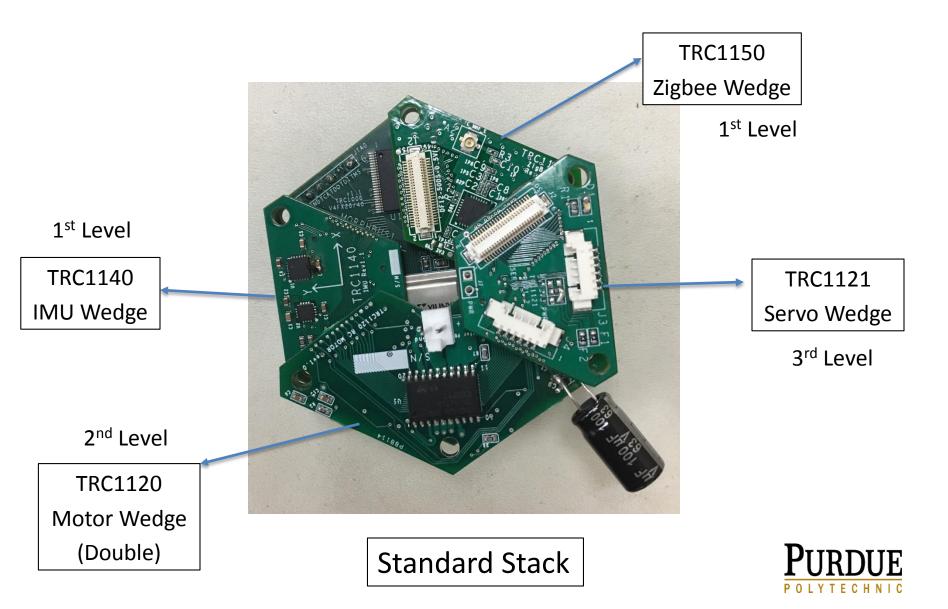

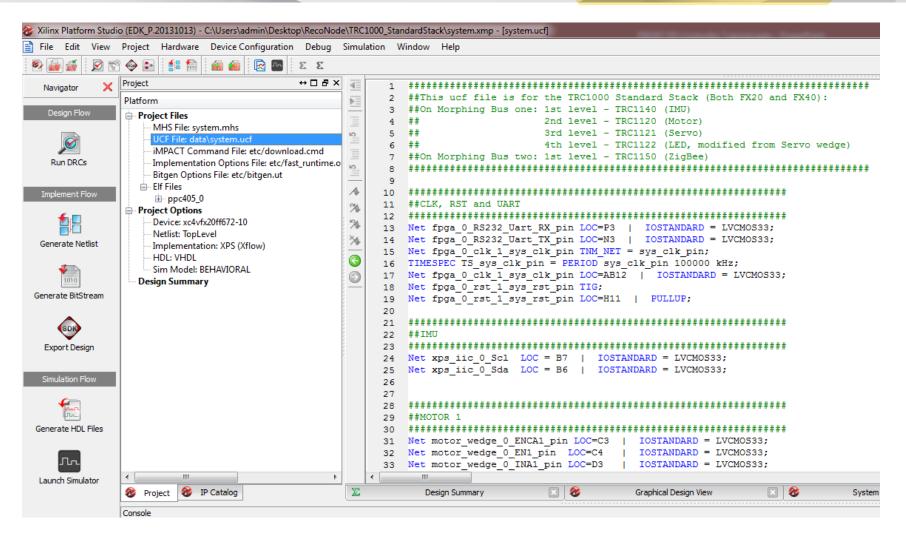

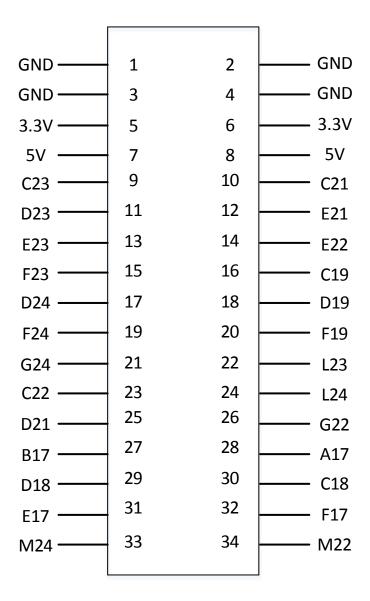

### 1. Hardware Setup – MorphingBus

#### Standard I/O Stack

RecoNode has two MorphingBus connectors where you can stack I/O wedges in a double-helix.

The *CRL Standard Stack* is composed of Morphing Bus 1 (left in Fig)

- TRC1140 IMU Wedge (1<sup>st</sup> level)

- TRC1120 Motor Wedge (2<sup>nd</sup> level)

- TRC1121 Servo Wedge (3<sup>rd</sup> level) Morphing Bus 2 (right in Fig)

- TRC1150 Zigbee Wedge (1<sup>st</sup> level)

However, you can customize your stack and change the number & order of the I/O wedges. Different projects use different I/O configurations and the FPGA configuration in the XPS must reflect the physical stack.

### 1. Hardware Setup – Standard I/O Stack

### 2. Copy an Existing Project

### First, let's install ISE 14.7 software from Xilinx.

### 2. Installation of Software

#### Multi-File Download: ISE Design - 14.7 Full Product Installation

| <ul> <li>Last Updated October 2013</li> <li>As of October 2013, ISE has moved into the sustaining phase of its product life cycle, and there are no more planned ISE releases.</li> <li>ISE supports the following devices families and their previous generations: Spartan-6, Virtex-6, and Coolrunner. For more</li> </ul> | Download Includes | ISE Design Suite (All Editions)<br>Lab Tools: Standalone<br>Installation<br>Platform Studio and Embedded<br>Development Kit<br>Software Development Kit<br>(SDK)<br>System Generator for DSP |               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| information, visit the ISE Design Suite                                                                                                                                                                                                                                                                                      | Download Type     | Full Product Installation                                                                                                                                                                    |               |

| Xilinx recommends Vivado Design Suite for new design starts                                                                                                                                                                                                                                                                  | Last Updated      | Oct 23, 2013                                                                                                                                                                                 |               |

| with Virtex-7, Kintex-7, Artix-7, and Zynq-7000.                                                                                                                                                                                                                                                                             | Answers           | 14.7 - Release Notes<br>ISE Design Suite 14 - Known<br>Issues                                                                                                                                |               |

| All Platforms - Split Installer Base Image - File 1/4 (TAR/GZIP -                                                                                                                                                                                                                                                            | Enablement        | License Solution Center                                                                                                                                                                      |               |

| 1.95 GB)<br>MD5 SUM Value: ff0f8a08aba2b7110fa730c6b15067d6                                                                                                                                                                                                                                                                  | Order DVD         | ISE Design Suite DVD                                                                                                                                                                         |               |

| L Install Data A - File 2/4 (ZIP - 1.97 GB)<br>MD5 SUM Value: c0962036464ff6b772b20c032b2f954b                                                                                                                                                                                                                               |                   |                                                                                                                                                                                              |               |

| Linstall Data B - File 3/4 (ZIP - 1.97 GB)<br>MD5 SUM Value: e6146a7eac7c026b4b507fdfb7549e4e                                                                                                                                                                                                                                |                   | Download Xilinx design to<br><u>https://www.xilinx.com/si</u><br><u>ad/index.html/content/xil</u><br>adNav/design-tools.html                                                                 | upport/downlo |

| Install Data C - File 4/4 (ZIP - 1.98 GB)<br>MD5 SUM Value: 90943813f27a083e8929f3e742416417                                                                                                                                                                                                                                 |                   |                                                                                                                                                                                              |               |

If they ask for licenses, input this to "path to license": <u>2100@marina.ecn.purdue.edu</u> (purchased by Dr. Richard M. Voyles for CRL), (Last update 12/12/2016)

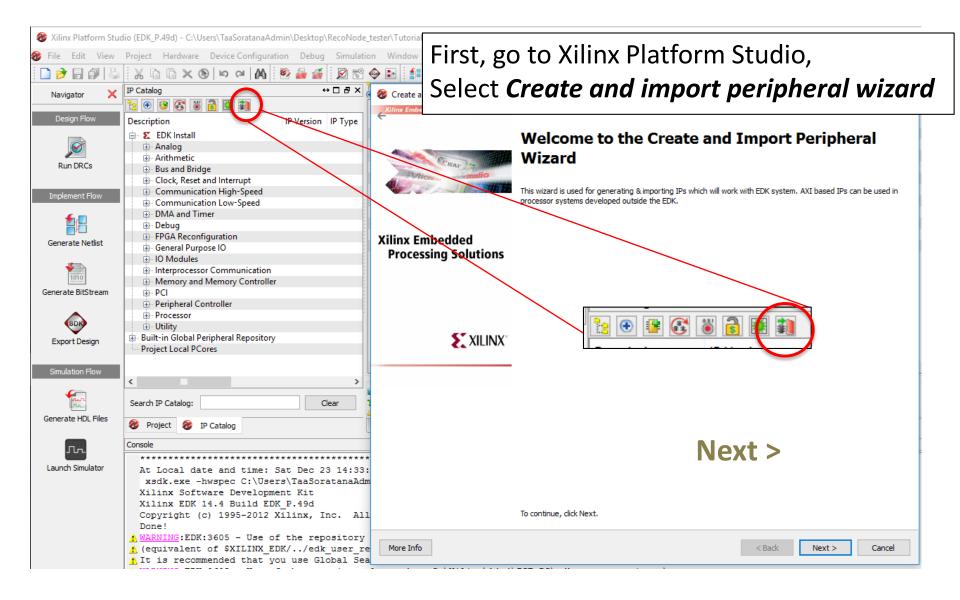

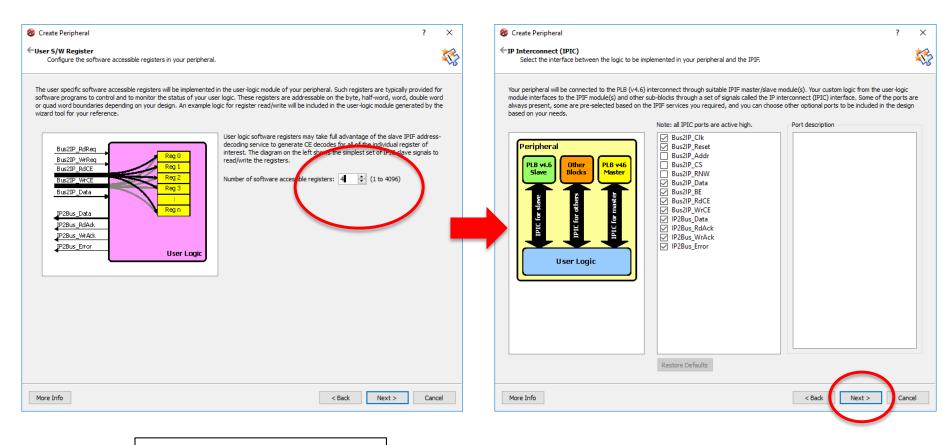

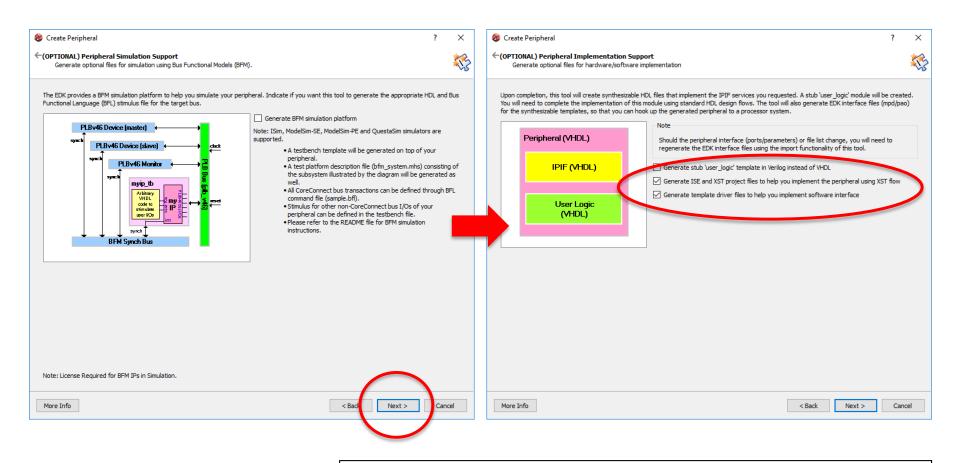

#### 2. A. Test the Project

- a. Open on Xilinx Platform Studio

- b. Import the Project to Xilinx SDK

- c. Program the Hardware

# We will program the hardware with an existing project and test it.

## **OPEN EXISTING PROJECT WITH XPS**

- a. Xilinx Platform Studio (XPS) Provides Hardware Configuration Tools

- The XPS allows the configuration of the FPGA hardware

- VHDL and Verilog code can be written for custom logic

- IP cores can be embedded from the Xilinx library

- Signals can be routed to different pins

### 2. A. a. Xilinx Platform Studio

| Co v kecoNode          | ► TRC1000_StandardStack ►                           |                   |                     |       |

|------------------------|-----------------------------------------------------|-------------------|---------------------|-------|

| Organize 🔻 💼 Open      | <ul> <li>Share with </li> <li>New folder</li> </ul> |                   |                     |       |

|                        |                                                     |                   |                     |       |

| 🚖 Favorites            | Name                                                | Date modified     | Туре                | Size  |

| 🧮 Desktop              | 鷆 .metadata                                         | 7/9/2018 6:39 PM  | File folder         |       |

| 🗼 Downloads            | 鷆xps                                                | 7/9/2018 7:20 PM  | File folder         |       |

| 🖳 Recent Places        | 鷆 data                                              | 7/9/2018 6:29 PM  | File folder         |       |

| 🗇 A360 Drive           | 퉬 etc                                               | 7/9/2018 6:29 PM  | File folder         |       |

|                        | 鷆 hdi                                               | 7/9/2018 6:29 PM  | File folder         |       |

| 门 Libraries            | ) implementation                                    | 7/9/2018 6:36 PM  | File folder         |       |

| Documents              | 퉬 pcores                                            | 7/9/2018 6:30 PM  | File folder         |       |

| 🌙 Music                | 鷆 revup                                             | 7/9/2018 6:36 PM  | File folder         |       |

| Pictures               | 퉬 SDK                                               | 7/9/2018 6:29 PM  | File folder         |       |

| 🗐 Subversion           | 퉬 software                                          | 7/9/2018 6:29 PM  | File folder         |       |

| 🛃 Videos               | 퉬 synthesis                                         | 7/9/2018 6:29 PM  | File folder         |       |

|                        | ]] TRC1000_StandardStack_hw_platform                | 7/9/2018 7:24 PM  | File folder         |       |

| 👰 Computer             | clock_generator_0.log                               | 12/12/2014 11:07  | wrifile             | 1 KB  |

| 🏭 Local Disk (C:)      | 📄 platgen.log                                       | 12/12/2014 11:07  | wrifile             | 19 KB |

| 👝 Local Disk (D:)      | 📄 platgen.opt                                       | 12/12/2014 11:07  | OPT File            | 1 KB  |

| 👝 SANGJUN (H:)         | psf2Edward.log                                      | 12/12/2014 11:07  | wrifile             | 1 KB  |

| 🙀 montgom6 (\\myhc     | SDK.log                                             | 7/10/2018 1:39 PM | wrifile             | 4 KB  |

| 🚽 voyleslab (\\techsto | system.bsb                                          | 12/12/2014 11:07  | BSB File            | 2 KB  |

| 🔊 A360 Drive           | system.log                                          | 7/10/2018 5:50 PM | wrifile             | 3 KB  |

|                        | system.make                                         | 7/9/2018 7:20 PM  | MAKE File           | 8 KB  |

| 📬 Network              | system.mhs                                          | 12/12/2014 11:07  | MHS File            | 8 KB  |

|                        | 🍪 system.xmp                                        | 7/9/2018 6:37 PM  | Xilinx Platform Stu | 1 KB  |

|                        | system_incl.make                                    | 7/9/2018 7:20 PM  | MAKE File           | 4 KB  |

|                        | test.log                                            | 7/9/2018 6:38 PM  | wrifile             | 0 KB  |

|                        | Version_Changes.log                                 | 7/9/2018 6:37 PM  | wrifile             | 1 KB  |

|                        | 📄 xdsgen.log                                        | 12/12/2014 11:07  | wrifile             | 4 KB  |

|                        |                                                     |                   |                     |       |

We are starting with an existing project, so all logic has been already defined.

Open the existing \*.xmp file so we can export the hardware definition to the software environment.

Date modified: 7/9/2018 6:37 PM Xilinx Platform Studio Project Size: 535 bytes

system.xmp

Date created: 7/9/2018 6:29 PM

### 2. A. a. Xilinx Platform Studio

#### 🗞 Xilinx Platform Studio (EDK\_P.20131013) - C:\Users\admin\Desktop\RecoNode\TRC1000\_StandardStack\system.xmp - [System Assembly View]

🍪 File Edit View Project Hardware Device Configuration Debug Simulation Window Help

i 🔊 🚐 🚄 i 🏹 🗠 🗛 🖪 i 🚛 🛱 i 🚑 🚑 i 🕞 🐻 i 🗴 😴

| Vavigator 🛛 🗙     | IP Catalog               | 2          |         |        | + 🗆                                | P ×                                   |               | Bus Interfaces  | Ports       | Addresses      |               |                                      |              |      |

|-------------------|--------------------------|------------|---------|--------|------------------------------------|---------------------------------------|---------------|-----------------|-------------|----------------|---------------|--------------------------------------|--------------|------|

| 1                 | 1                        |            |         |        |                                    | B                                     |               | Name            | Bus Name    |                | Туре          | IP Version                           |              |      |

| Design Flow       | Description              | IP Version | IP Type | Status | Processor Suppor IP Classification | 880                                   |               | plb             |             |                | plb_v46       | 1.05.a                               |              |      |

|                   | 🖨 🐮 EDK Install          |            |         |        |                                    |                                       |               | ppc405_0        |             |                | ppc405_virt   |                                      |              |      |

| S                 | Analog                   |            |         |        |                                    |                                       | - <b>-</b>    | plb_bram_if     |             |                | bram_block    |                                      |              |      |

| *                 | Arithmetic               |            |         |        |                                    |                                       | - K-          | 😟 xps_bram_if   |             |                | xps_bram_if   |                                      |              |      |

| Run DRCs          | Bus and Bridge           |            |         |        |                                    | - I K-                                |               | itagppc_cnt     |             |                | jtagppc_cntlr |                                      |              |      |

|                   | Clock, Reset and Interru |            |         |        |                                    |                                       |               | 😑 motor_wed     |             |                | motor_wed     | 1.10.a                               |              |      |

| nplement Flow     | Communication High       |            |         |        |                                    | <b>.</b>                              |               |                 | plb         |                |               |                                      |              |      |

| npiement now      | Communication Low-S      |            |         |        |                                    |                                       | <del>~ </del> | proc_sys_re     |             | - 📩 📩          | proc_sys_re   |                                      |              |      |

| <b>4 •</b>        | DMA and Timer            |            |         |        |                                    |                                       |               | ia cc2520_reset |             |                | xps_gpio      | 2.00.a                               |              |      |

| 1                 | Debug                    |            |         |        |                                    |                                       |               | SPLB            | plb         |                |               |                                      |              |      |

|                   | FPGA Reconfiguration     |            |         |        |                                    |                                       |               | 🖨 led           |             | <del></del>    | xps_gpio      | 2.00.a                               |              |      |

| enerate Netlist   | General Purpose IO       |            |         |        |                                    |                                       |               | SPLB            | plb         | -              |               |                                      |              |      |

|                   | IO Modules               |            |         |        |                                    |                                       |               | ⊕ xps_iic_0     |             |                | xps_iic       | 2.03.a                               |              |      |

| - <b>*</b>        | Interprocessor Commu     |            |         |        |                                    |                                       | -             | 🖨 xps_spi_0     |             | - 📩 📩          | xps_spi       | 2.02.a                               |              |      |

| 1010              | Memory and Memory        |            |         |        |                                    |                                       |               | SPLB            | plb         |                |               |                                      |              |      |

| nerate BitStream  | ⊕ PCI                    |            |         |        |                                    |                                       |               | 🖨 xps_timer_0   |             | - 📩 📩          | xps_timer     | 1.02.a                               |              |      |

|                   | Peripheral Controller    |            |         |        |                                    |                                       |               | SPLB            | plb         | -              |               |                                      |              |      |

|                   | Processor                |            |         |        |                                    |                                       | -             | 🖨 xps_timer_1   |             | - 📩 📩          | xps_timer     | 1.02.a                               |              |      |

| SDK               | Utility                  |            |         |        |                                    |                                       |               | SPLB            | plb         | -              |               |                                      |              |      |

| Export Design     | Project Local PCores     |            |         |        |                                    |                                       |               | 🖨 xps_timer_2   |             | - 📩 📩          | xps_timer     | 1.02.a                               |              |      |

| LADOI ( D'Ebigi i |                          |            |         |        |                                    |                                       |               | SPLB            | plb         | -              |               |                                      |              |      |

|                   |                          |            |         |        |                                    |                                       |               | 🖨 xps_timer_3   |             | - 📩 📩          | xps_timer     | 1.02.a                               |              |      |

| imulation Flow    |                          |            |         |        |                                    | i 🎍 🚽                                 |               | SPLB            | plb         | -              |               |                                      |              |      |

|                   |                          |            |         |        |                                    |                                       |               | 😑 xps_timer_4   |             | - 📩 📩          | xps_timer     | 1.02.a                               |              |      |

| <b>4</b>          |                          |            |         |        |                                    | • • • • • • • • • • • • • • • • • • • |               | SPLB            | plb         | -              |               |                                      |              |      |

| The second        |                          |            |         |        |                                    |                                       |               | 🖨 xps_timer_5   |             | - 📩 📩          | xps_timer     | 1.02.a                               |              |      |

| nerate HDL Files  |                          |            |         |        |                                    |                                       |               | SPLB            | plb         | -              |               |                                      |              |      |

|                   |                          |            |         |        |                                    |                                       |               | 😑 xps_timer_6   |             | - 📩 📩          | xps_timer     | 1.02.a                               |              |      |

|                   |                          |            |         |        |                                    |                                       |               | SPLB            | plb         | -              |               |                                      |              |      |

| л                 |                          |            |         |        |                                    |                                       |               | 🖨 xps_timer_7   |             | - 📩 📩          | xps_timer     | 1.02.a                               |              |      |

| unch Simulator    |                          |            |         |        |                                    | Legend                                |               |                 |             |                |               |                                      |              |      |

|                   | Search IP Catalog:       |            |         |        | Clear                              |                                       |               |                 |             |                |               | onnected M Monit<br>duction 🕸 Beta 🚝 |              | nt   |

|                   | Scarch IF Catalog.       |            |         |        | Clear                              |                                       |               | Discontinued    | icense (eva | , <u>~</u> L00 |               |                                      | a sveropiner |      |

|                   | 🍪 Project 🍪 IP Catalog   |            |         |        |                                    | 2                                     |               | gn Summary      | × (         | 3              | Graphical Des | ign View                             | 🗙 🗞          | Syst |

|                   | Console                  |            |         |        |                                    |                                       |               |                 |             |                |               |                                      |              |      |

|                   |                          |            |         |        |                                    |                                       |               |                 |             |                |               |                                      |              |      |

### 2. A. a. Xilinx Platform Studio

| 🍪 Xilinx Platform Studio                                                                           | o (EDK_P.20131013) - C:\Users\admin\Desktop\RecoNode'                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| File Edit View                                                                                     | Project Hardware Device Configuration Debug S                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 🕺 🎑 🍯 🕺 😒                                                                                          | 🛛 🛛 🖾 🔜 📾 📾 📾 🔤 🗠                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Navigator 🗙                                                                                        | Project ↔ □ ♂ ×                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Design Flow<br>Run DRCs<br>Implement Flow<br>Generate Netlist                                      | Platform            → Project Files         → MHS File: system.ucf         → UCF File: data\system.ucf         → iMPACT Command File: etc/download.cmd         → Implementation Options File: etc/fast_runtime.o         → Bitgen Options File: etc/bitgen.ut         → Elf Files         ⊕→ ppc405_0             → Project Options         → Device: xc4vfx20ff672-10         → Netlist: TopLevel         → Implementation: XPS (Xflow)         → HDL: VHDL         → Sim Model: BEHAVIORAL         → Design Summary |

| Generate BitStream<br>Export Design<br>Simulation Flow<br>Generate HDL Files<br>Generate HDL Files | < □□□ ►                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

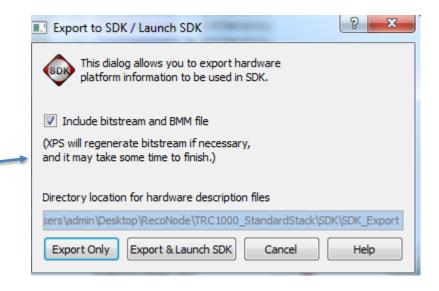

We want to export the existing design and launch the SDK.

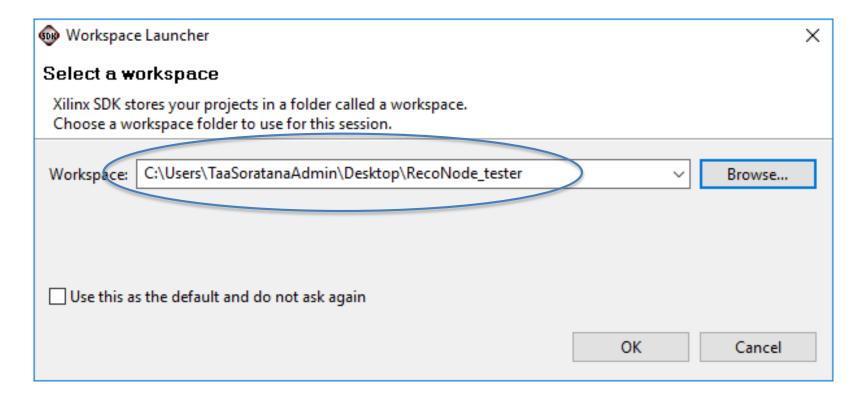

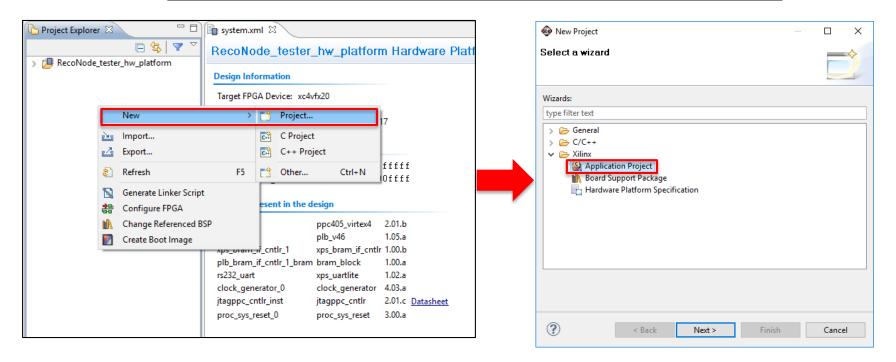

#### **b.** Import the Project to Xilinx SDK

| <ul> <li>SOLIDWORKS Installation Manager</li> <li>Startup</li> <li>Texas Instruments</li> <li>TI Emulators</li> <li>TortoiseSVN</li> <li>VideoLAN</li> <li>WinDirStat</li> <li>Windows Kits</li> </ul> | Open Xilinx Software Development Kit (SDK)<br>and select the same workspace that contains<br>your <i>.xmp</i> file |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| \mu WinPcap                                                                                                                                                                                            |                                                                                                                    |

| 🐌 Wolfram Mathematica 🛛 🛛 🚳                                                                                                                                                                            | Workspace Launcher                                                                                                 |

| 🐌 Xilinx Design Tools                                                                                                                                                                                  |                                                                                                                    |

| 🐌 ISE Design Suite 14.7 Se                                                                                                                                                                             | lect a workspace                                                                                                   |

| 🐌 Accessories 🛛 🗸 🕺                                                                                                                                                                                    | ilinx SDK stores your projects in a folder called a workspace.                                                     |

| 📙 ChipScope Pro 🛛 🖉 📿                                                                                                                                                                                  | hoose a workspace folder to use for this session.                                                                  |

| Documentation                                                                                                                                                                                          |                                                                                                                    |

| 📙 EDK 🛛 🖊 👘 🛛 🗤                                                                                                                                                                                        | /orkspace: C:\Users\admin\Desktop\RecoNode\TRC1000_StandardStack                                                   |

| 🎯 Xilinx Platform Studio 🧹 🚊                                                                                                                                                                           |                                                                                                                    |

| Xilinx Software Development                                                                                                                                                                            |                                                                                                                    |

| 📙 Documentation 🦳                                                                                                                                                                                      |                                                                                                                    |

| 🌗 Tools 🛛 👻                                                                                                                                                                                            |                                                                                                                    |

| ◀ Back                                                                                                                                                                                                 | Use this as the default and do not ask again                                                                       |

| Search programs and files                                                                                                                                                                              | OK Cancel                                                                                                          |

| The second secon                                                                                                                                                                                                                                                                                                                                   |        | 🚳 Import                                                                                                       |                                                                                                             | Click "Dro                                                | "   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|-----|

| Select<br>Create new projects from an archive file or directory.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Ľ      | Import Projects<br>Select a directory to sea                                                                   | rch for existing Eclipse projects.                                                                          | Click "Bro                                                | wse |

| Select an import source:<br>type filter text<br>General<br>Chick File<br>Existing Projects into Workspace<br>File System<br>Preferences<br>C/C++<br>C/C++<br>C/C++ Execut ble<br>C/C++ Project Settings<br>Existing Code as Makefile Project<br>Existing Code as Makefile Project<br>C/C++<br>Existing Code as Makefile Project<br>Existing Code as Makefile Project<br>C/C++<br>C/C++<br>Existing Code as Makefile Project<br>Existing Code as Makefile Project<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C++<br>C/C |        | Select root directory:     Select <u>a</u> rchive file:     Projects: <u>Copy projects in     Working cote</u> | rowse For Folder                                                                                            | Browse<br>Browse<br>Select All<br>Deselect All<br>Refresh |     |

| > 🦻 Team                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        | C:\Us                                                                                                          |                                                                                                             | ktop\RecoNode<br>ware\SDK\SDK                             |     |

| Rack Next > Finish                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Cancel | ?                                                                                                              | SDK     Software     SDK                                                                                    | Ξ                                                         |     |

| Continue with                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |        |                                                                                                                | SDK_Export                                                                                                  |                                                           |     |

| "Existing Projects into Works                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | pace"  |                                                                                                                | <ul> <li>Fivebar_nodeA</li> <li>Fivebar_nodeA</li> <li>Fivebar_nodeA</li> <li>Folder: SDK_Export</li> </ul> | _bsp                                                      |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |        |                                                                                                                | Make New Folder                                                                                             | OK Cancel                                                 |     |

Include in library 🔻

RecoNode ► TRC1000\_StandardStack ► software ► SDK ► SDK\_Export ►

| 0 | ra | а | n | IZ | e |  |

|---|----|---|---|----|---|--|

|   |    | _ |   |    | _ |  |

Share with 💌 New folder

| 쑦 Favorites       | Name                              | Date modified     | Туре        | Size |  |

|-------------------|-----------------------------------|-------------------|-------------|------|--|

| 🧾 Desktop         | 🌗 .metadata                       | 2/8/2018 9:15 PM  | File folder |      |  |

| 🗼 Downloads       | 🌗 fivebar_nodeA                   | 2/8/2018 9:15 PM  | File folder |      |  |

| 🗐 Recent Places   | 🌗 fivebar_nodeA_bsp               | 2/8/2018 9:15 PM  | File folder |      |  |

| A360 Drive        | 🌗 fivebar_nodeB                   | 2/8/2018 9:15 PM  | File folder |      |  |

|                   | 🌗 fivebar_nodeB_bsp               | 2/8/2018 9:16 PM  | File folder |      |  |

| 🥽 Libraries       | 퉬 fivebar_oneNode_twoMotor        | 2/8/2018 9:15 PM  | File folder |      |  |

| Documents         | 퉬 fivebar_oneNode_twoMotor_bsp    | 2/8/2018 9:15 PM  | File folder |      |  |

| 🎝 Music           | PBORT_menu_tutorial               | 2/9/2018 12:47 AM | File folder |      |  |

| Pictures          | PBORT_menu_tutorial2              | 2/9/2018 12:26 AM | File folder |      |  |

| 🗐 Subversion      | TRC1000_StandardStack_hw_platform | 2/8/2018 9:15 PM  | File folder |      |  |

| 📑 Videos          | 퉬 zigbee_multicast                | 2/8/2018 9:16 PM  | File folder |      |  |

|                   | 퉬 zigbee_multicast_bsp            | 2/8/2018 9:15 PM  | File folder |      |  |

| 🜉 Computer        | 퉬 zigbee_one2one                  | 2/8/2018 9:16 PM  | File folder |      |  |

| 🏭 Local Disk (C:) | 퉬 zigbee_one2one_bsp              | 6/27/2018 3:22 PM | File folder |      |  |

|                   |                                   |                   |             |      |  |

C:\Users\admin\Desktop\RecoNode\TRC1000 \_StandardStack\software\SDK\SDK\_Export Contains all existing tested project folders.

💼 Network

A360 Drive

Local Disk (D:) SANGJUN (H:) 🙀 montgomб (\\myhc

🖵 voyleslab (\\techsto

| 💀 Import                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                  |                                                        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|--------------------------------------------------------|

| Import Projects  Some projects cannot be imported because they already exist in the workspace                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                  |                                                        |

| Select root directory: C:\Users\admin\Desktop\RecoNode\TRC1000_'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Browse                                                                           |                                                        |

| <ul> <li>Select <u>a</u>rchive file:</li> <li><u>P</u>rojects:</li> <li>fivebar_nodeA (C:\Users\admin\Desktop\RecoNode\TRC1000_ ^</li> <li>fivebar_nodeA_bsp (C:\Users\admin\Desktop\RecoNode\TRC1</li> <li>fivebar_nodeB (C:\Users\admin\Desktop\RecoNode\TRC1000</li> <li>fivebar_nodeB_bsp (C:\Users\admin\Desktop\RecoNode\TRC1</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | B <u>r</u> owse<br><u>S</u> elect All<br><u>D</u> eselect All<br><u>Re</u> fresh |                                                        |

| fivebar_oneNode_twoMotor (C:\Users\admin\Desktop\RecoNd<br>fivebar_oneNode_twoMotor_bsp (C:\Users\admin\Desktop\Re<br>PIORT_menu_tutorial (C:\Users\admin\Desktop\RecoNode\Tf<br>PBORT_menu_tutorial (C:\Users\admin\Desktop\RecoNode\Tf<br>minimized to the total to | 5                                                                                | Select the project folders that rou want to import.    |

| Copy projects into workspace Working sets Add project to working sets Working sets:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                  | For this tutorial, we want PBORT_menu_tutorial folder. |

| (?) < <u>B</u> ack <u>N</u> ext > <u>F</u> inish                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Cancel                                                                           | PURDUE<br>POLYTECHNIC                                  |

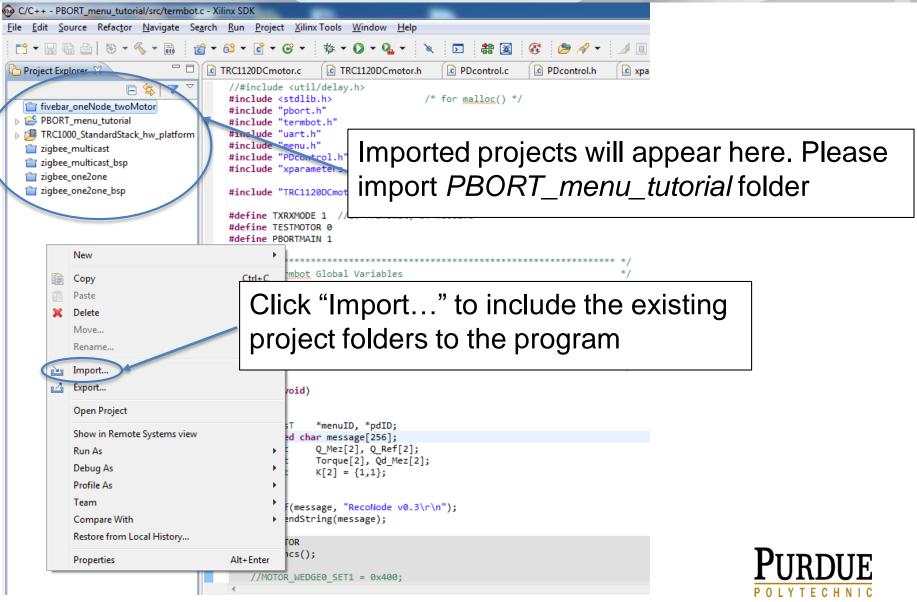

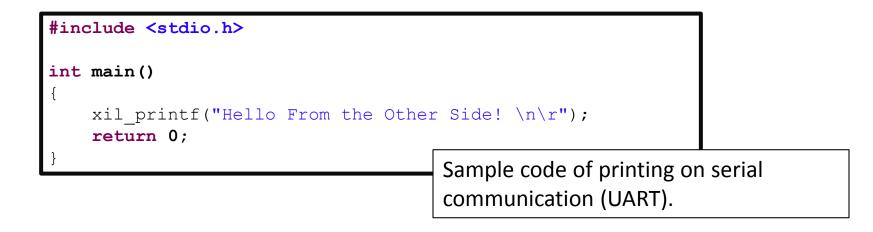

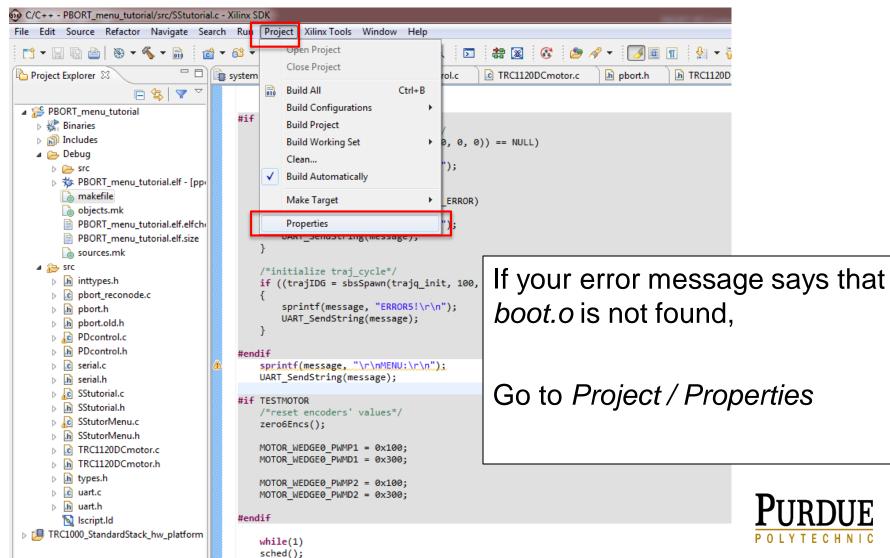

Description

#### C/C++ - PBORT\_menu\_tutorial/src/termbot.c - Xilinx SDK File Edit Source Refactor Navigate Search Run Project Xilinx Tools Window Help 😤 i 🎓 🛷 🛨 📑 • 🗑 🖻 🕘 • 🔨 • 🛗 👩 • 🚳 • 🕑 • 🞯 • 🖉 • 🖉 • 🖉 • 🖉 28 🐹 🌛 🔲 🗊 🕴 🖢 🖛 🌾 TRC1120DCmotor.c 눱 Project Explorer 🙁 TRC1120DCmotor.h PDcontrol.c C PDcontrol.h xparameters.h termbo //#include <util/delay.h> $\nabla$ 雪川 #include <stdlib.h> /\* for malloc() \*/ fivebar oneNode twoMotor #include "pbort.h" 🞏 PBORT menu tutorial #include "termbot.h" #include "uart.h" Binaries #include "menu.h" Includes #include "PDcontrol.h" b > > Debug #include "xparameters.h" // newly added SE 🔺 🗁 src Inttypes.h #include "TRC1120DCmotor.h" b c menu.c #define TXRXMODE 1 //1: Transmit, 0: Receive b h menu.h #define TESTMOTOR 0 b bort\_reconode.c #define PBORTMAIN 1 b h pbort.h b h pbort.old.h D PDcontrol.c Termbot Global Variables D PDcontrol.h b c serial.c b h serial.h b c termbot.c b h termbot.h /\* Termbot Routines CRAWLER CRAWLER CRAWLER TRC1120DCmotor.c TRC1120DCmotor.h h types.h ⊖ int main (void) Open an existing project and b ic uart.c h uart.h processT \*menuID, \*pdID; 🔊 Iscript.ld you will see all c files in src unsigned char message[256]; TRC1000 StandardStack hw platform $\triangleright$ int32 t Q\_Mez[2], Q\_Ref[2]; zigbee\_multicast int32 t Torque[2], Qd Mez[2]; folder. zigbee\_multicast\_bsp int16 t $K[2] = \{1,1\};$ zigbee\_one2one zigbee\_one2one\_bsp sprintf(message, "RecoNode v0.3\r\n"); UART SendString(message); #if TESTMOTOR zero6Encs(); //MOTOR WEDGE0 SET1 = 0x400; 💦 Problems 🖾 🖉 Tasks) 💻 Console) 🔲 Properties) 🧶 Terminal 1) 🐹 XMD Console 0 items

Resource

Path

Location

Type

```

ALL COMPANY

uint8 t tmpLo;

unsigned char message[256];

/* look for incoming serial commands*/

if (!UART Empty()){

tmp = UART_GetByte();

#if 0

/* echo the character, show the command*/

🖳 Problems 🗖 Tasks 📃 Console 🖾

🗧 🔲 Properties 🖉 Terminal

CDT Build Console [PBORT_menu_tutorial]

errences room mena tacoriarrer

Scanaar ascact in practoring

elfcheck

Xilinx EDK 14.7 Build EDK P.20131013

Copyright (c) 1995-2012 Xilinx, Inc. All rights reserved.

Command Line: elfcheck -hw ../../TRC1000 StandardStack hw platform/system.xml

-pe ppc405 0 PBORT menu tutorial.elf

ELF file

: PBORT menu tutorial.elf

elfcheck passed.

Save the changes you made

'Finished building: PBORT menu tutorial.elf.elfcheck'

on the code, xilinx will

16:05:46 Build Finished (took 2s.427ms)

automatically compile and

generate elf file.

```

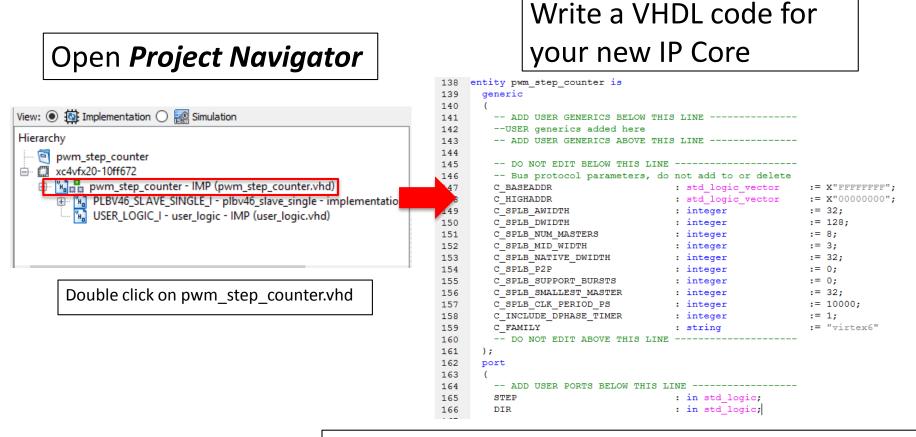

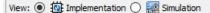

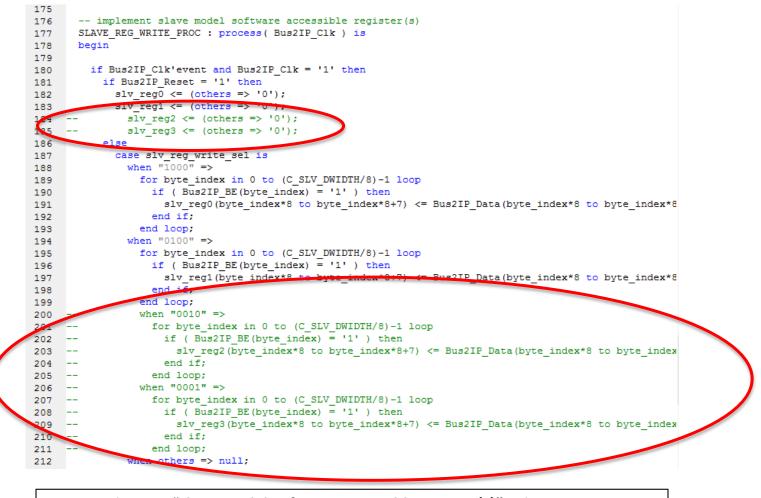

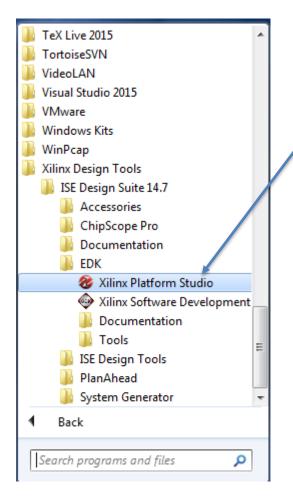

ь